- 您现在的位置:买卖IC网 > Sheet目录3841 > PIC24FJ128GA008-I/PT (Microchip Technology)IC PIC MCU FLASH 128K 80TQFP

2005-2012 Microchip Technology Inc.

DS39747F-page 101

PIC24FJ128GA010 FAMILY

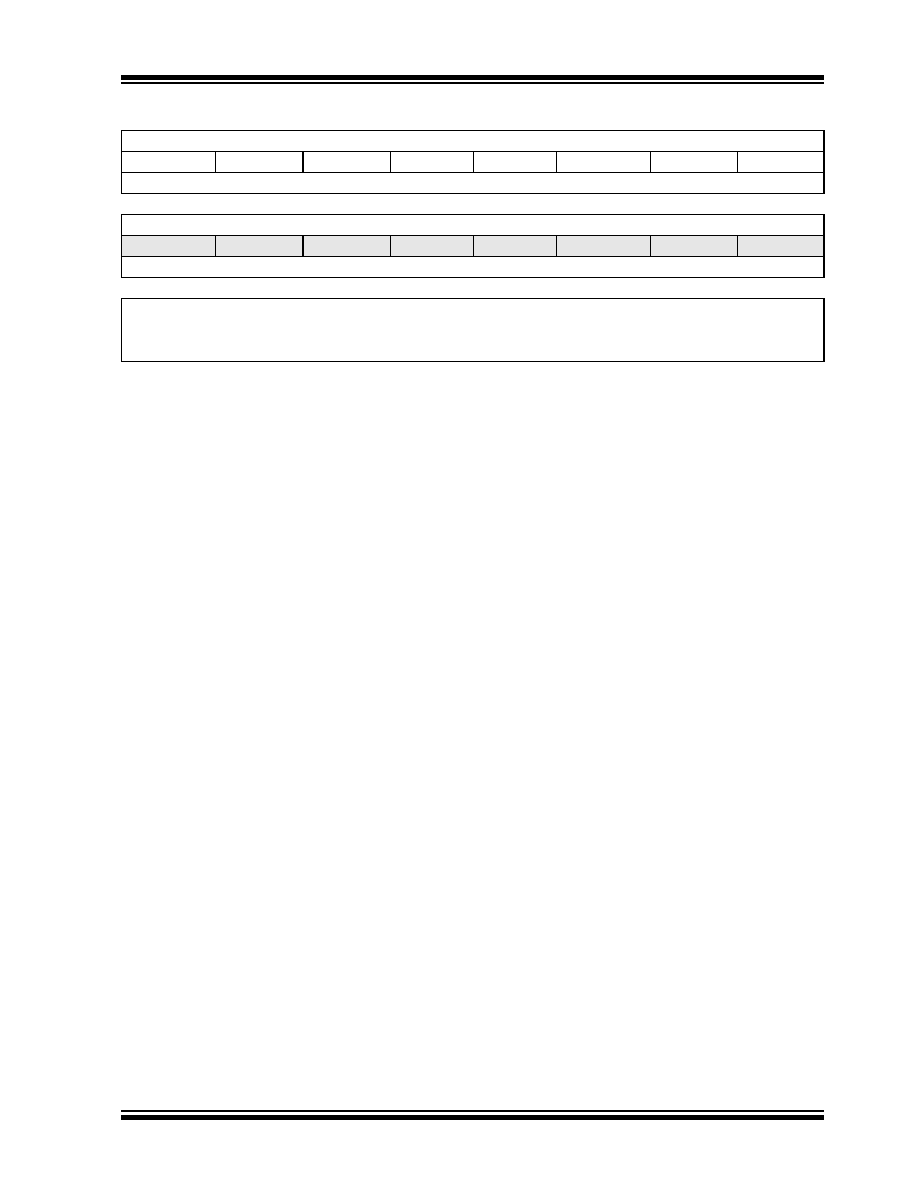

REGISTER 8-2:

CLKDIV: CLOCK DIVIDER REGISTER

R/W-0

R/W-1

ROI

DOZE2

DOZE1

DOZE0

DOZEN(1)

RCDIV2

RCDIV1

RCDIV0

bit 15

bit 8

U-0

—

bit 7

bit 0

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as ‘0’

-n = Value at POR

‘1’ = Bit is set

‘0’ = Bit is cleared

x = Bit is unknown

bit 15

ROI:

Recover on Interrupt bit

1

= Interrupts clear the DOZEN bit and reset the CPU peripheral clock ratio to 1:1

0

= Interrupts have no effect on the DOZEN bit

bit 14-12

DOZE<2:0>:

CPU Peripheral Clock Ratio Select bits

111

= 1:128

110

= 1:64

101

= 1:32

100

= 1:16

011

= 1:8

010

= 1:4

001

= 1:2

000

= 1:1

bit 11

DOZEN:

DOZE Enable bit(1)

1

= DOZE<2:0> bits specify the CPU peripheral clock ratio

0

= CPU peripheral clock ratio set to 1:1

bit 10-8

RCDIV<2:0>:

FRC Postscaler Select bits

111

= 31.25 kHz (divide-by-256)

110

= 125 kHz (divide-by-64)

101

= 250 kHz (divide-by-32)

100

= 500 kHz (divide-by-16)

011

= 1 MHz (divide-by-8)

010

= 2 MHz (divide-by-4)

001

= 4 MHz (divide-by-2)

000

= 8 MHz (divide-by-1)

bit 7-0

Unimplemented:

Read as ‘0’

Note 1:

This bit is automatically cleared when the ROI bit is set and an interrupt occurs.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16F737-I/SP

IC PIC MCU FLASH 4KX14 28DIP

PIC18F86K22-I/PTRSL

MCU PIC 64K FLASH XLP 80TQFP

PIC16C63A-04I/SP

IC MCU OTP 4KX14 PWM 28DIP

PIC16C63A-04I/SO

IC MCU OTP 4KX14 PWM 28SOIC

52559-2270

CONN FFC 22POS .5MM VERT ZIF SMD

52559-1870

CONN FFC 18POS .5MM VERT ZIF SMD

DSPIC33EP64MC506-I/PT

IC DSC 16BIT 64KB FLASH 64TQFP

52745-1896

CONN FFC 18POS .5MM R/A ZIF SMD

相关代理商/技术参数

PIC24FJ128GA008T-I/PF

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:64/80/100-Pin General Purpose, 16-Bit Flash Microcontrollers

PIC24FJ128GA008T-I/PT

功能描述:16位微控制器 - MCU 128KB 69I/O RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24FJ128GA010

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:General Purpose, 16-Bit Flash Microcontrollers

PIC24FJ128GA010_09

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:64/80/100-Pin General Purpose, 16-Bit Flash Microcontrollers

PIC24FJ128GA010_12

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:64/80/100-Pin, General Purpose, 16-Bit Flash Microcontrollers

PIC24FJ128GA010-I/PF

功能描述:16位微控制器 - MCU 16 Bit 128KB Flash 8Kb RAM 53 I/O RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24FJ128GA010-I/PT

功能描述:16位微控制器 - MCU 128KB 84 I/O RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24FJ128GA010T-I/PF

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:64/80/100-Pin General Purpose, 16-Bit Flash Microcontrollers